想象一下,一枚芯片上集成了记忆和计算的能力,在保护用户隐私同时,还具备了类似人脑的自主学习,能耗仅为先进工艺下专用集成电路系统的1/35,听起来是不是很神奇?

据清华大学公众号10月9日消息,近期,清华大学集成电路学院教授吴华强、副教授高滨基于存算一体计算范式,研制出全球首颗全系统集成的、支持高效片上学习(机器学习能在硬件端直接完成)的忆阻器存算一体芯片,在支持片上学习的忆阻器存算一体芯片领域取得重大突破,有望促进人工智能、自动驾驶可穿戴设备等领域的发展。

该研究成果日前发表在《科学》上。

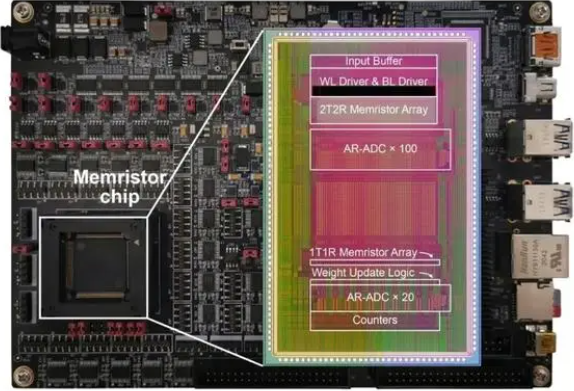

忆阻器存算一体学习芯片及测试系统 (图片来源:清华大学)

记忆电阻器,是继电阻、电容、电感之后的第四种电路基本元件。它可以在断电之后,仍能“记忆”电阻状态,被当做新型纳米电子突触器件。

面向传统存算分离架构制约算力提升的重大挑战,吴华强、高滨聚焦忆阻器存算一体技术研究,探索实现计算机系统新范式。

忆阻器存算一体技术在底层器件、电路架构和计算范式上全面颠覆了冯·诺依曼传统计算架构,可实现算力和能效的跨越式提升,同时,该技术还可利用底层器件的学习特性,支持实时片上学习,赋能基于本地学习的边缘训练新场景。

课题组基于存算一体计算范式,创造性提出适配忆阻器存算一体实现高效片上学习的新型通用算法和架构,通过算法、架构、集成方式的全流程协同创新,研制出全球首颗全系统集成的、支持高效片上学习的忆阻器存算一体芯片。

忆阻器芯片的研发面临着技术挑战和工程挑战。

据了解,忆阻器芯片的研发涉及到材料科学、物理学、电子工程等多学科的前沿知识。在诸多技术难题中,首先要解决的是如何实现忆阻器件的大规模集成。通过大量实验和理论研究,团队提出了架构-电路-工艺协同优化方法,为存算一体系统的设计提供了指导。

有了大规模集成的工艺、关键的电路设计,如何克服底层多尺度非理想导致的误差,集合成一个高效的系统芯片?在团队老师和学生的共同努力下,研究提出STELLAR 架构,完成算法优化及仿真实验,制备出全系统集成的高效存算一体学习芯片,实现速度和能效的大幅提升。

放眼未来,吴华强希望团队的方案、技术能够走出实验室,切切实实推动科研成果转化,致力服务国家所需、社会所需。

来源:每日经济新闻

dxeditor12

未经允许不得转载:财富在线 » 清华大学重磅消息:我国芯片领域取得重大突破!

财富在线

财富在线 财富在线:突然,强势拉升,商业航天板块爆发

财富在线:突然,强势拉升,商业航天板块爆发 财富在线:大湾研究丨坚定看好AI产业发展

财富在线:大湾研究丨坚定看好AI产业发展 财富在线午评:“开门红”延续,这两个板块共20股涨停!

财富在线午评:“开门红”延续,这两个板块共20股涨停! 【财富在线午后看点】光纤供需收紧头部受益,二线厂商估值有待修复

【财富在线午后看点】光纤供需收紧头部受益,二线厂商估值有待修复 【财富在线热点聚焦】PCB涨停潮!覆铜板交货延至六周,AI服务器引爆需求

【财富在线热点聚焦】PCB涨停潮!覆铜板交货延至六周,AI服务器引爆需求 财富在线:2026商业航天看什么?六大核心逻辑拆解

财富在线:2026商业航天看什么?六大核心逻辑拆解 财富在线午评:节后“马上红”!半导体多股20CM涨停

财富在线午评:节后“马上红”!半导体多股20CM涨停 财富在线:5月商业航天任务“日程满满”,这些大事值得期待

财富在线:5月商业航天任务“日程满满”,这些大事值得期待

评论前必须登录!

登陆 注册